# **Microcomputer Components**

8-Bit CMOS Microcontroller

C501GV

**3 V Specification**

Addendum to the C501 Data Sheet 06.97

**Advance Information**

#### Edition 06.97

Published by Siemens AG, Bereich Halbleiter, TS Balanstraße 73, 81541 München

© Siemens AG 1997. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

#### **Absolute Maximum Ratings**

| Ambient temperature under bias $(T_A)$<br>Storage temperature $(T_{ST})$                                                           |     |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Voltage on $V_{\rm CC}$ pins with respect to ground ( $V_{\rm SS}$ )<br>Voltage on any pin with respect to ground ( $V_{\rm SS}$ ) |     |

| Input current on any pin during overload condition                                                                                 |     |

| Power dissipation                                                                                                                  | TBD |

#### Note:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage of the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for longer periods may affect device reliability. During overload conditions ( $V_{IN} > V_{CC}$  or  $V_{IN} < V_{SS}$ ) the Voltage on  $V_{CC}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### **DC Characteristics**

$V_{\rm CC}$  = 3.3 V + 0.3V, - 0.6V;  $V_{\rm SS}$  = 0 V;  $T_{\rm A}$  = 0 to + 70 °C

| Parameter                                            | Symbol           | Limi                | Limit Values          |    | Test Condition                   |

|------------------------------------------------------|------------------|---------------------|-----------------------|----|----------------------------------|

|                                                      |                  | min.                | max.                  |    |                                  |

| Input low voltage                                    | $V_{IL}$         | - 0.5               | 0.8                   | V  | _                                |

| Input high voltage                                   | $V_{IH}$         | 2.0                 | V <sub>CC</sub> + 0.5 | V  | -                                |

| Output low voltage                                   |                  |                     |                       |    |                                  |

| Ports 1, 2, 3                                        | $V_{OL1}$        | -                   | 0.45                  | V  | $I_{\rm OL} = 1.6  {\rm mA^{1}}$ |

| Port 0, EA, RESET                                    | $V_{OL2}$        | -                   | 0.45                  | V  | $I_{\rm OL} = 3.2 {\rm mA^{1)}}$ |

| Ports 1, 2, 3                                        | $V_{OL3}$        | -                   | 0.3                   | V  | $I_{\rm OL} = 100 \ \mu A^{1}$   |

| Port 0, EA, RESET                                    | $V_{OL4}$        | -                   | 0.3                   | V  | $I_{\rm OL} = 200 \ \mu A^{-1}$  |

| Output high voltage                                  |                  |                     |                       |    |                                  |

| Ports 1, 2, 3                                        | V <sub>OH1</sub> | 2.0                 | _                     | V  | $I_{OH} = -20 \mu A$             |

|                                                      | V <sub>OH2</sub> | 0.9 V <sub>CC</sub> | _                     | V  | $I_{\rm OH} = -10 \mu \text{A}$  |

| Port 0 in external bus mode,                         |                  |                     |                       |    | ,                                |

| ALE, PSEN                                            | $V_{OH3}$        | 2.0                 | _                     | V  | $I_{\rm OH} = -800 \ \mu A^{2}$  |

|                                                      | $V_{OH4}$        | 0.9 V <sub>cc</sub> | _                     | V  | $I_{\rm OH} = -80 \ \mu A^{2}$   |

| Logic 0 input current<br>(Ports 1, 2, 3)             | I                | - 1                 | - 50                  | μA | $V_{\rm IN} = 0.45 \ { m V}$     |

| Logical 1-to-0 transition current<br>(Ports 1, 2, 3) | I <sub>TL</sub>  | - 25                | - 250                 | μA | V <sub>IN</sub> = 2.0 V          |

| Input leakage current                                |                  |                     |                       |    |                                  |

| Port 0, EA                                           | $I_{LI}$         | -                   | ± 1                   | μA | $0.45 < V_{\rm IN} < V_{\rm CC}$ |

| Pin capacitance 6)                                   | C <sub>IO</sub>  | _                   | 10                    | pF | $f_{\rm C}$ = 1 MHz              |

|                                                      |                  |                     |                       |    | $T_{\rm A} = 25 \ {\rm °C}$      |

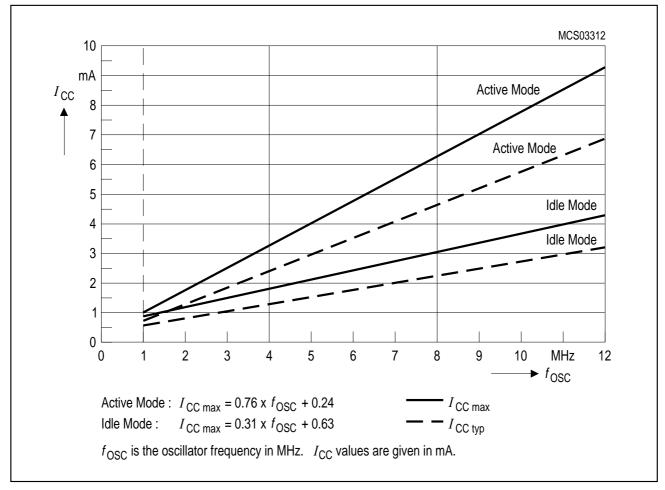

#### **Power Supply Current**

| Parameter                | Symbol          | Lin  | nit Values | Unit | Test Condition                       |

|--------------------------|-----------------|------|------------|------|--------------------------------------|

|                          |                 | typ. | max.       |      |                                      |

| Power supply current: 7) |                 |      |            |      |                                      |

| Active mode, 12 MHz      | I <sub>cc</sub> | 6.9  | 9.4        | mA   | 4)                                   |

| Idle mode, 12 MHz        | I <sub>CC</sub> | 3.2  | 4.4        | mA   | 5)                                   |

| Power Down Mode          | I <sub>PD</sub> | -    | 15         | μA   | $V_{\rm CC}$ = 2 3.6 V <sup>3)</sup> |

#### Notes :

- <sup>1)</sup> Capacitive loading on ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub> of ALE and port 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operation. In the worst case (capacitive loading : > 50 pF), the noise pulse on ALE line may exceed 0.8 V. In such cases it may be desirable to qualify ALE with a schmitt-trigger, or use an address latch with a schmitt-trigger strobe input.

- <sup>2)</sup> Capacitive loading on ports 0 and 2 may cause the  $V_{OH}$  on ALE and  $\overline{PSEN}$  to momentarily fall bellow the  $V_{IL}$  specification when the address lines are stabilizing.

- <sup>3)</sup>  $I_{PD}$  (Power Down Mode) is measured under following conditions:  $\overline{EA} = Port0 = V_{CC}$ ; RESET =  $V_{SS}$ ; XTAL2 = N.C.; XTAL1 =  $V_{SS}$ ; all other pins are disconnected.

- <sup>4)</sup> I<sub>CC</sub> (active mode) is measured with: XTAL1 driven with t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V, V<sub>IH</sub> = V<sub>CC</sub> - 0.5 V; XTAL2 = N.C.; EA = Port0 = RESET = V<sub>CC</sub>; all other pins are disconnected. I<sub>CC</sub> would be slightly higher if a crystal oscillator is used (appr. 1 mA).

- <sup>5)</sup>  $I_{CC}$  (Idle mode) is measured with all output pins disconnected and with all peripherals disabled; XTAL1 driven with  $t_{CLCH}$ ,  $t_{CHCL} = 5$  ns,  $V_{IL} = V_{SS} + 0.5$  V,  $V_{IH} = V_{CC} - 0.5$  V; XTAL2 = N.C.; RESET =  $\overline{EA} = V_{SS}$ ; Port0 =  $V_{CC}$ ; all other pins are disconnected; where  $f_{OSC}$  is the oscillator frequency in MHz.  $I_{CC}$  values are given in mA and measured at  $V_{CC} = 3.3$  V.

- <sup>6)</sup> This parameter is periodically sampled and not 100% tested.

- <sup>7)</sup> The typical  $I_{CC}$  values are periodically measured at  $T_A = +25$  °C and  $V_{CC} = 3.0$  V but not 100% tested. The maximum  $I_{CC}$  values are measured under worst case conditions ( $V_{CC} = 3.6$  V,  $T_A = 0$  °C).

#### **ICC Diagram**

#### **AC Characteristics**

$V_{CC}$  = 3.3 V + 0.3V, - 0.6V;  $V_{SS}$  = 0 V,  $T_A$  = 0 °C to + 70 °C ( $C_L$  for port 0, ALE and PSEN outputs = 50 pF;  $C_L$  for all other outputs = 40 pF)

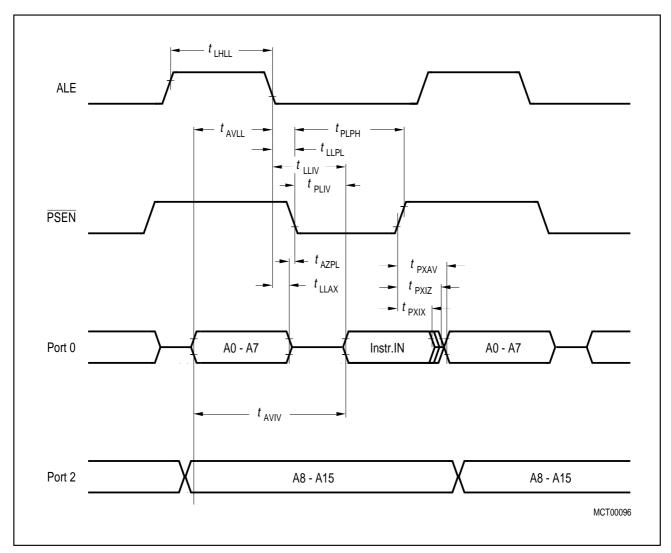

#### **Program Memory Characteristics**

| Parameter                          | Symbol                   | Limit Values    |      |                                                         |                                  |    |

|------------------------------------|--------------------------|-----------------|------|---------------------------------------------------------|----------------------------------|----|

|                                    |                          | 12 MHz<br>Clock |      | Variable Clock<br>1/t <sub>CLCL</sub> = 1 MHz to 12 MHz |                                  | _  |

|                                    |                          | min.            | max. | min.                                                    | max.                             | 1  |

| ALE pulse width                    | t <sub>LHLL</sub>        | 127             | -    | $2t_{CLCL} - 40$                                        | -                                | ns |

| Address setup to ALE               | t <sub>AVLL</sub>        | 43              | -    | $t_{\rm CLCL} - 40$                                     | -                                | ns |

| Address hold after ALE             | t <sub>LLAX</sub>        | 30              | -    | $t_{\rm CLCL} - 53$                                     | -                                | ns |

| ALE low to valid instr in          | t <sub>LLIV</sub>        | -               | 233  | -                                                       | $4t_{CLCL} - 100$                | ns |

| ALE to PSEN                        | t <sub>LLPL</sub>        | 58              | -    | <i>t</i> <sub>CLCL</sub> – 25                           | -                                | ns |

| PSEN pulse width                   | t <sub>PLPH</sub>        | 215             | -    | $3t_{CLCL} - 35$                                        | -                                | ns |

| PSEN to valid instr in             | t <sub>PLIV</sub>        | -               | 150  | -                                                       | $3t_{CLCL} - 100$                | ns |

| Input instruction hold after PSEN  | t <sub>PXIX</sub>        | 0               | -    | 0                                                       | -                                | ns |

| Input instruction float after PSEN | $t_{PXIZ}^{*)}$          | -               | 63   | -                                                       | $t_{\rm CLCL} - 20$              | ns |

| Address valid after PSEN           | t <sub>PXAV</sub> *)     | 75              | -    | $t_{\rm CLCL} - 8$                                      | -                                | ns |

| Address to valid instr in          | <i>t</i> <sub>AVIV</sub> | -               | 302  | -                                                       | 5 <i>t</i> <sub>CLCL</sub> – 115 | ns |

| Address float to PSEN              | t <sub>AZPL</sub>        | 0               | -    | 0                                                       | -                                | ns |

\*) Interfacing the C501 microcontrollers to devices with float times up to 75 ns is permissible. This limited bus contention will not cause any damage to port 0 drivers.

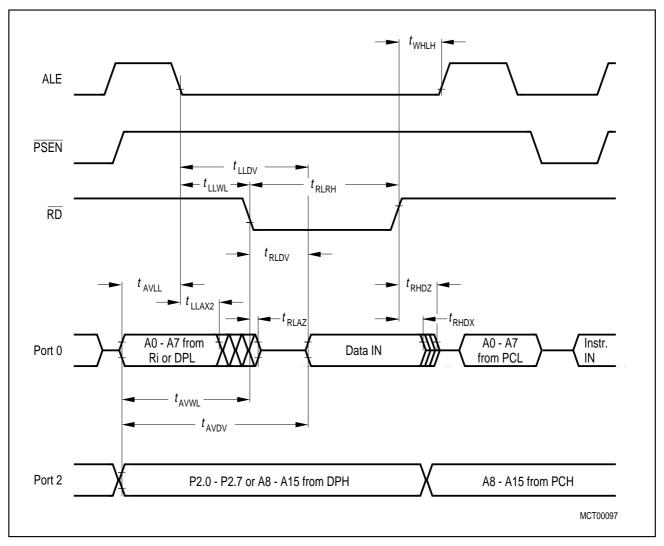

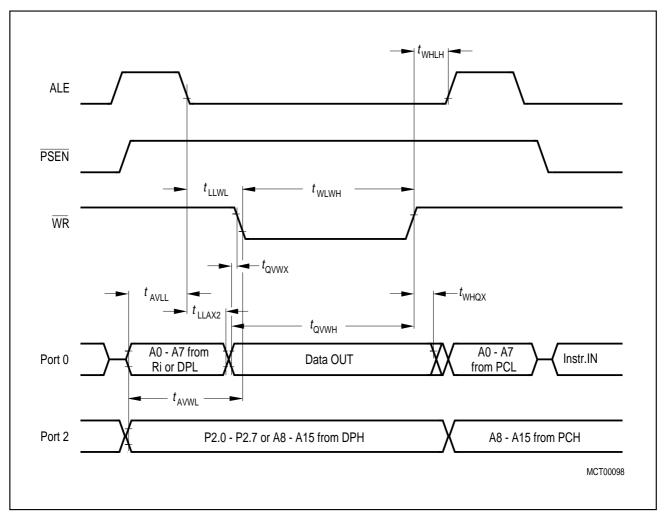

## **External Data Memory Characteristics**

| Parameter                                                         | Symbol                   | Limit Values    |      |                                                         |                                  |    |

|-------------------------------------------------------------------|--------------------------|-----------------|------|---------------------------------------------------------|----------------------------------|----|

|                                                                   |                          | 12 MHz<br>Clock |      | Variable Clock<br>1/t <sub>CLCL</sub> = 1 MHz to 12 MHz |                                  |    |

|                                                                   |                          | min.            | max. | min.                                                    | max.                             | 1  |

| RD pulse width                                                    | t <sub>RLRH</sub>        | 400             | -    | 6 <i>t</i> <sub>CLCL</sub> – 100                        | -                                | ns |

| WR pulse width                                                    | t <sub>wLWH</sub>        | 400             | -    | $6t_{CLCL} - 100$                                       | -                                | ns |

| Address hold after ALE                                            | t <sub>LLAX2</sub>       | 30              | -    | <i>t</i> <sub>CLCL</sub> – 53                           | -                                | ns |

| RD to valid data in                                               | t <sub>RLDV</sub>        | -               | 252  | -                                                       | 5 <i>t</i> <sub>CLCL</sub> – 165 | ns |

| Data hold after RD                                                | t <sub>RHDX</sub>        | 0               | -    | 0                                                       | -                                | ns |

| Data float after RD                                               | t <sub>RHDZ</sub>        | -               | 97   | -                                                       | $2t_{\text{CLCL}} - 70$          | ns |

| ALE to valid data in                                              | t <sub>LLDV</sub>        | -               | 517  | -                                                       | $8t_{CLCL} - 150$                | ns |

| Address to valid data in                                          | <i>t</i> <sub>AVDV</sub> | -               | 585  | -                                                       | 9 <i>t</i> <sub>CLCL</sub> – 165 | ns |

| ALE to $\overline{WR}$ or $\overline{RD}$                         | t <sub>LLWL</sub>        | 200             | 300  | $3t_{CLCL} - 50$                                        | $3t_{CLCL}$ + 50                 | ns |

| Address valid to $\overline{WR}$ or $\overline{RD}$               | <i>t</i> <sub>AVWL</sub> | 203             | -    | $4t_{CLCL} - 130$                                       | -                                | ns |

| $\overline{\text{WR}}$ or $\overline{\text{RD}}$ high to ALE high | t <sub>WHLH</sub>        | 43              | 123  | $t_{\rm CLCL} - 40$                                     | $t_{\text{CLCL}} + 40$           | ns |

| Data valid to WR transition                                       | t <sub>QVWX</sub>        | 33              | -    | $t_{\rm CLCL} - 50$                                     | -                                | ns |

| Data setup before WR                                              | t <sub>QVWH</sub>        | 433             | -    | 7 <i>t</i> <sub>CLCL</sub> – 150                        | -                                | ns |

| Data hold after WR                                                | t <sub>WHQX</sub>        | 33              | -    | <i>t</i> <sub>CLCL</sub> – 50                           | -                                | ns |

| Address float after RD                                            | t <sub>RLAZ</sub>        | -               | 0    | -                                                       | 0                                | ns |

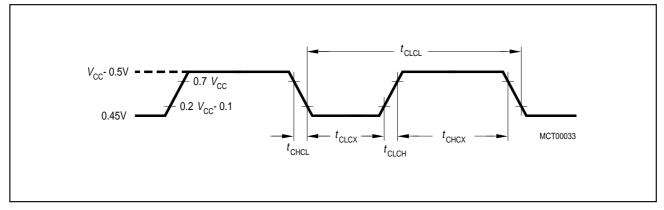

### **External Clock Characteristics**

| Parameter         | Symbol            |      | Unit                          |    |

|-------------------|-------------------|------|-------------------------------|----|

|                   |                   |      |                               |    |

|                   |                   | min. | max.                          |    |

| Oscillator period | t <sub>CLCL</sub> | 83.3 | 1000                          | ns |

| High time         | t <sub>CHCX</sub> | 20   | $t_{\rm CLCL} - t_{\rm CLCX}$ | ns |

| Low time          | t <sub>CLCX</sub> | 20   | $t_{\rm CLCL} - t_{\rm CHCX}$ | ns |

| Rise time         | t <sub>CLCH</sub> | -    | 20                            | ns |

| Fall time         | t <sub>CHCL</sub> | -    | 20                            | ns |

# SIEMENS

## Program Memory Read Cycle

# SIEMENS

Data Memory Read Cycle

# SIEMENS

**Data Memory Write Cycle**

External Clock Drive at XTAL2

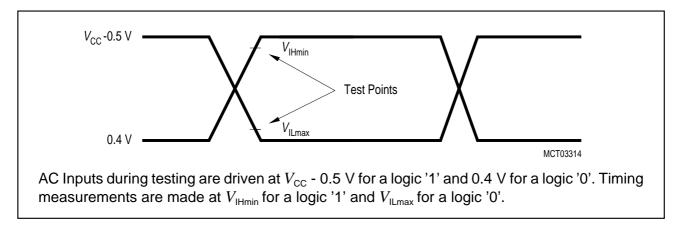

#### AC Testing: Input, Output Waveforms

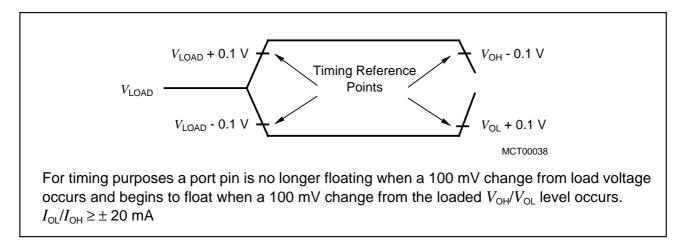

#### **AC Testing: Float Waveforms**

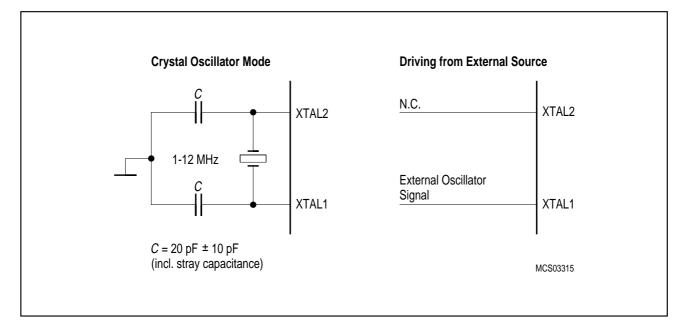

#### **Recommended Oscillator Circuits for Crystal Oscillator**

## **Ordering Information**

| Туре                           | Ordering Code                | Package | Description<br>(8-Bit CMOS microcontroller) |

|--------------------------------|------------------------------|---------|---------------------------------------------|

| SAB-C501GV-LN<br>SAB-C501GV-LP | Q67120-C2017<br>Q67120-C2016 |         | for external memory (12 MHz)                |